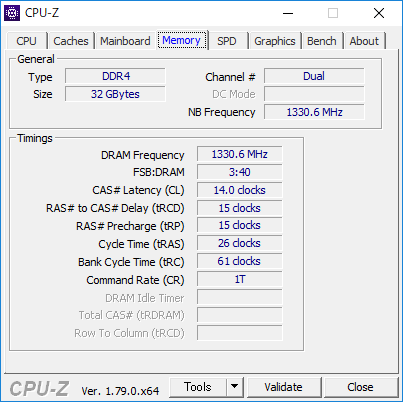

4本差しで利用しているQ4U2666BME-8G(BLE8G4D26AFEA)ですが、最適なtRASの値がネット上の情報だけではいまいちわからなかったため自分で計測してみました。

発端

メモリタイミング最適値の計算式を完全に理解しているわけではありませんが、tRASの値は少なくともCL+tRCD₊αを設定しないといけないと思っていました。実際、AEGESA1.0.0.4a未満の頃はDDR4メモリが高クロックで動作しない場合はtRASを緩めろとアドバイスしているサイトもあるくらいです。

ところがメモリタイミングのセッティングをしている際、入力を間違ってtRASにCL+tRCD以下の値を入力してしまってもOSが起動してしまったではないですか!

tRASは詰めれば良いというものではないのかもしれません。ならば最適なtRAS値を求めてデータを取ってみようという企画です。

AIDA64でメモリレイテンシを取得する

メモリベンチをなるべく簡単に計測するためAIDA64 Extreme(5.90.4200)をTRIALで使用します。

ベンチはリード/ライト/リライト/レイテンシの4種類を取得可能ですが、リード~リライトはCL値よりも動作クロックの影響が大きいので「レイテンシ」を使用します。ブレをなるべく減らすため試行回数は10回。tRAS値はOSが普通に起動した28から、AGESA1.0.0.4a公開前にとあるショップが推奨していた39までと、BIOSで設定可能な最も大きな値58を試します。

tRAS毎のレイテンシ

この10回の最低値・最高値・変動幅・中央値・平均値を表にすると以下の通り。最も低いレイテンシが出たtRAS=33だけは、偶発的な値でないか確認するためにもう1セット追加計測しています。

| tRAS | レイテンシ(ns) | ||||

|---|---|---|---|---|---|

| 最低値 | 最高値 | 変動幅 | 中央値 | 平均値 | |

| 28 | 82 | 84.3 | 2.3 | 82.85 | 82.95 |

| 29 | 81.6 | 83.9 | 2.3 | 82.45 | 82.45 |

| 30 | 81.8 | 83.3 | 1.5 | 82.5 | 82.5 |

| 31 | 81.8 | 82.9 | 1.1 | 82.55 | 82.46 |

| 32 | 81.7 | 83.3 | 1.6 | 82.55 | 82.57 |

| 33 | 81.7 | 82.8 | 1.1 | 82.05 | 82.19 |

| 33 (2回目) |

81.3 | 82.7 | 1.4 | 82.25 | 82.14 |

| 34 | 81.5 | 83.4 | 1.9 | 82.6 | 82.45 |

| 35 | 82 | 83.6 | 1.6 | 82.55 | 82.58 |

| 36 | 82 | 83.7 | 1.7 | 82.8 | 82.8 |

| 37 | 81.9 | 82.8 | 0.9 | 82.4 | 82.4 |

| 38 | 81.4 | 83.2 | 1.8 | 82.4 | 82.37 |

| 39 | 82.1 | 83.4 | 1.3 | 82.7 | 82.75 |

| 58 | 81.8 | 84.3 | 2.5 | 82.45 | 82.67 |

縦に長くて見づらいので折れ線グラフにします。

tRAS値考察

ざっくり分析すると「tRAS値のレイテンシへの影響は極わずか。安定稼働する値ならなんでもOK」としか言えません。

もう少し掘り下げてみると「CL+tRCD未満でもとりあえず動作する。他と比べて確実に遅いが気にするほどの差はない」「Q4U2666BME-8G⁺RYZEN+AGESA1.0.0.4aの場合はtRAS=33が最適」ということくらいでしょうか。

とりあえずtRAS33で利用することにします。